差分晶振在高速 FPGA 上的应用

2025-07-10

差分晶振在高速 FPGA 设计中具有非常重要的应用,尤其是在对时钟精度、抗干扰能力、信号完整性要求高的系统中,比如:

- 高速串行接口(PCIe、SFP+/QSFP、10G Ethernet、DDR4/DDR5)

- 多通道数据采集系

- 高速通信系统(SerDes)

- 精确同步系统(时间戳、ADC/DAC 驱动)

一、什么是差分晶振?

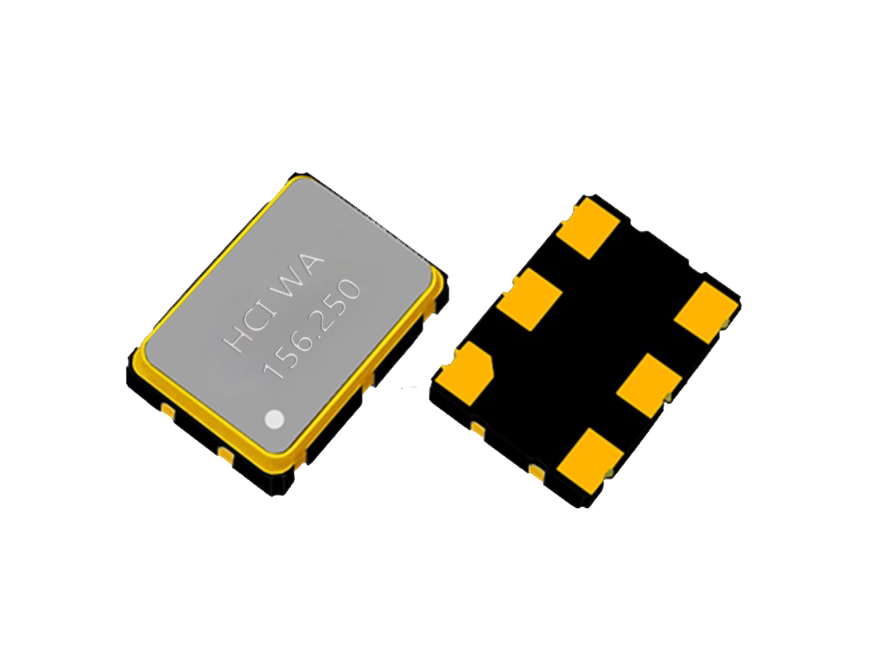

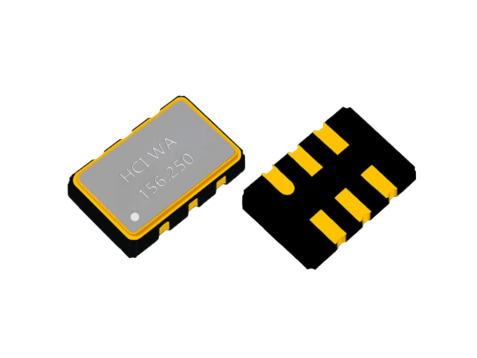

差分晶振(Differential Oscillator)是一种输出差分信号(如 LVDS、LVPECL、HCSL)的有源晶体振荡器,其输出两个互为反相的时钟信号(CLK+ 和 CLK−)。它不同于传统的单端晶振(如 CMOS 输出的 Oscillator)。

二、差分信号的优势:

特性 | 差分信号 | 单端信号 |

抗干扰能力 | 强(共模噪声抵消) | 弱 |

信号完整性 | 好,易于传输高速信号 | 差 |

驱动能力 | 高,适合远距离/高速传输 | 低 |

抖动性能 | 更低 | 相对较高 |

三、差分晶振在高速 FPGA 上的应用

1. 作为高速接口参考时钟

PCIe、10G/25G Ethernet、SATA 等高速接口必须使用差分参考时钟;

通常使用 100 MHz 或 156.25 MHz 差分晶振(如 HCSL/LVDS 输出);

FPGA 内部的 GTX/GTH/GTP 等高速收发器模块(Transceivers) 需要这些差分参考时钟。

典型连接:

差分晶振 → FPGA GTREFCLK0/1(高速收发器参考时钟引脚)

2. 时钟树的核心时钟源

多通道高速系统中,使用差分晶振驱动一个时钟分配芯片(如 SI5341/AD9528),再输出多个同步时钟;

适用于多 ADC、DAC、FPGA 通信时钟对齐。

结构示意:

差分晶振 → 时钟管理芯片(如 PLL / Fanout Buffer)

↓

多个同步时钟 → FPGA/ADC/DAC

3. 驱动 FPGA 内部 PLL/MMCM

差分晶振可用于提供高品质时钟输入(如通过 IBUFDS 接口进入 FPGA),再由内部 PLL/MMCM 输出系统各模块时钟;提升时钟质量,降低整体系统时钟抖动。

常见差分输出类型与 FPGA 兼容性

输出类型 | 典型应用 | FPGA 接口兼容性 |

LVDS | 通用差分晶振输出类型 | 所有主流 FPGA 支持(GTX/GTH 输入) |

HCSL | PCIe、服务器主板用 | 直接支持(如 Xilinx PCIe IP 核) |

LVPECL | 高频、高摆幅应用 | 需要外部终端匹配和偏置电阻 |

CML | 超高速链路(>10 Gbps) | 高端 FPGA 收发器支持 |

✔ 建议根据 FPGA 厂商推荐使用匹配的差分输出类型。

四、差分晶振选型建议

参数 | 建议值 |

频率稳定度 | ±25 ppm 或更优 |

相位抖动(12kHz–20MHz) | < 1ps RMS(高速接口要求) |

输出类型 | LVDS/HCSL 优先,取决于 FPGA 兼容性 |

负载能力 | 驱动能力 ≥ 15pF 或与时钟芯片匹配 |

温度范围 | 工业级(-40°C ~ +85°C)或更宽 |

优先选择协议推荐频率:

PCIe:100 MHz;

SFP+/10G Ethernet:156.25 MHz;

25G/40G Ethernet:312.5 MHz;

JESD204B/C:250 MHz、312.5 MHz、625 MHz 等。

参考 FPGA 官方文档推荐时钟范围;

抖动指标要低:

RMS jitter < 0.5 ps(高速接口要求);

特别重要于 PCIe、JESD204C、10G/25G Ethernet。

五、差分晶振在高速 FPGA 上的常用频率

频率(MHz) | 应用场景 | 备注 |

100 MHz | PCIe Gen1/Gen2;通用高速逻辑系统 | 非常常见,支持 HCSL/LVDS |

125 MHz | Gigabit Ethernet(千兆网) | 适用于 GMII、SGMII 等接口 |

156.25 MHz | 10G Ethernet(10GBASE-R/XAUI)、SFP+、QSFP、CEI 接口等 | 高速串行通信标准频率 |

200 MHz | DDR4 时钟、多速率收发器参考频率 | 通常用于倍频生成更高时钟 |

212.5 MHz | JESD204B/C 数据转换链路 | 高频采集通信接口标准频率 |

250 MHz | 高速 ADC/DAC 系统、部分 JESD204C 系统 | 抖动要求更严格 |

312.5 MHz | 25G Ethernet(25GBASE-R)、高速光通信系统 | 差分输出常为 CML/LVPECL |

322.265625 MHz | CPRI(6.144 Gbps)参考时钟 | 通信基站 FPGA 用 |

644.53125 MHz | CPRI(12.288 Gbps)、JESD204C 高速链路 | 极高速接口,需要极低抖动晶振 |

Others(用户自定义) | 特定频率输入给 PLL,再生成目标频率 | 需确认 PLL 支持倍频因子 |

✔ 具体型号建议联系杭晶销售或技术工程师 推荐使用匹配的差分输出类型。

六、总结

项目 | 差分晶振的优势 |

精度 | 抖动低,频率稳定 |

抗干扰 | 强,共模噪声抑制好 |

速度 | 支持 GHz 级高速传输 |

应用 | PCIe、SFP、DDR4/5、ADC、DAC、同步系统等 |

差分晶振在现代高速 FPGA 系统中几乎是标配,是确保系统高速通信与同步性能的关键器件。

如果你有具体的 FPGA 型号(如 Xilinx Zynq Ultrascale+、Intel Stratix 10)、差分晶振型号,或通信接口需求(如 PCIe Gen3/SFP+),苏州杭晶可以帮你推荐最合适的时钟配置方案与原理图连接设计。

晶振,差分晶振,高速 FPGA, FPGA,XO

扫一扫添加微信

扫一扫添加微信